当电路中信号能以要求的时序、持续时间和电压幅度到达IC时,该电路就有很好的信号完整性。当信号不能正常响应时,就出现了信号完整性问题。象误触发、阻尼振荡、过冲、欠冲等信号完整性问题会造成时钟间歇振荡和数据出错。为了正确识别和处理数据,IC要求数据在时钟边沿前后处于稳定状态,这个稳定状态的持续时间称为建立时间和保持时间。如果信号转变为不稳定状态或后来改变了状态,IC就可能误判或丢失部分数据。

信号的变化表现为IC管脚处的电压变化,这个电压的变化使IC的引脚发生状态变化。IC将数据或时钟作为信号送到电路板上的导体或导线上,这些数据或时钟信号必须在要求的时间内以一定的持续时间和电压到达导体或导线。当信号不满足上述条件时,SI问题就会出现,例如,由于导线的传播时延,信号到达导体或导线的过程产生了延时。当信号没有达到规定的电压时,IC状态不会改变。

由于信号欠冲,IC引脚的状态可能不确定。一般不希望信号达到规定电压后出现欠冲现象,它是由IC开关速度以及信号在导线上传输引起的。

电路板上的导线具有电阻、电容和电感等电气特性。在高频电路设计中,电路板线路上的电容和电感会使导线等效于一条传输线。传输线是所有导体及其接地回路的总和。传输线上的线路阻抗与外接负载不匹配会导致信号反射现象,从而引起信号完整性问题。电路的阻抗会使信号达不到规定的电压幅度从而影响信号完整性。

当信号压降太大时,信号电压可能不足以达到IC的开关门限,这时IC的状态就不会变化。此外,IC可能无法以恰当的时序识别输入数据或时钟。每个IC都有一个电压门限,超过这个电压门限就可判断IC管脚是高或低。对于IC的输入时钟来说,该状态可决定IC的输入管脚是否已做好接收数据的准备。如果IC无法处理时钟数据,则IC输入管脚在某一状态可能为“不确定”状态。

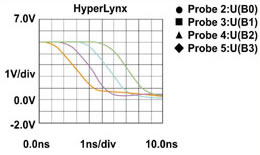

电子系统要求IC须按规定时序并在规定时间内接收数据,但传输线上的电容和电感会在驱动器高低切换和接收器高低切换之间产生时延,这种时延会影响IC的建立时间和保持时间,从而无法正确判断数据。对于依赖时序激活IC输入和输出的电路,延时问题会导致IC在错误的时钟周期内接收数据,这时就会引起间歇故障或错误的数据输出。

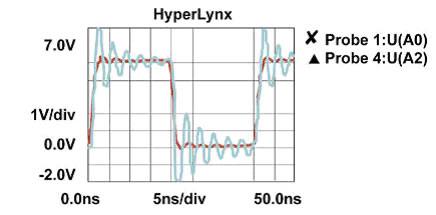

对于优良的SI设计来说,传输线路阻抗需要匹配它的外接负载。如果传输线阻抗和负载不匹配,信号的一部分能量就会反射回来,这种反射会导致信号过冲或欠冲,能量在驱动器与接收器之间不断重复反射时就会造成阻尼振荡。IC中的内部元件可以防止IC出现过压,因此过冲会对这些内部元件造成过压,如果电压太大并且重复作用的话,这些元件就可能损坏,从而造成整个IC失效。

IC的高低电平切换门限指的是信号从一个状态向另一个状态转换所需的电压值。当发生阻尼现象时,信号电平可能会超过IC输入脚的切换门限,从而将IC输入信号变为不确定状态,这会导致时钟出错或数据的错误接收。

上述SI问题还会影响那些本身没有SI问题的信号线。例如耦合可将串扰信号传导到邻近线路上,当耦合或串扰信号足够大时,接收串扰信号的线路就会出现信号完整性问题。串扰影响的不止是一条邻近线路,有时甚至会进而影响到其它相邻线路上的信号。