热点文章

技术文献

DF/SIGNOISE 应用解决PCB的SI问题

www.i-tech.com.cn 2013-11-17 上海泰齐科技网

【摘 要】

本文介绍了在通讯产品开发中,利用Cadence公司的DF/SigNoise信号完整性分析工具模 块解决 PCB 设计中存在的信号完整性(Signal Integrity)问题。

【关键词 】 PCB设计 信号完整性 (SI)

一、引言

当今通讯产业的蓬勃发展,得益于通讯产品的日新月异。高性能的产品开发,硬件设计,已不能仅靠年久的经验或器件使用说明来完成,工程师在设计高速数字信号传输系统时,要面临信号完整性(Signal Integrity)、电磁干扰(EMI)、时序(Timing)等问题,设计需要强 有力的EDA工具支持。DF/SigNoise是CADENCE公司的PCB信号完整性分析工具,可用于分析解决高速、高密度的互联线信号传输问题。本文介绍了利用Cadence公司的 DF/SigNoise 解 决通讯产品开发中,一块高密度、多负载PCB板总线网络存在的信号完整性问题,取得了较为满意的效果,解决了存在的信号质量问题,有效地缩短了产品开发周期。

二、PCB板的信号完整性仿真分析

1、硬件设计简介

图1为该板设计的主要总线网络结构,该板为系统中一主要的单板,数据总线、配置总线及使用的元器件很多,使得该板的密度较高。总线等网络的数据都是双向传输,且是点到多点,该板采用八层板结构,两层电源、地,六层信号。

2、信号存在问题及仿真分析

由于该板第一样板设计的时间短,使得设计中的器件选型和PCB的布局布线存在不足,第一板在测试中发现下列问题:总线网络中,近端负载信号波形在上升沿或下降沿上阈值处有畸变发生, 主要驱动器间的信号过冲很大等等。

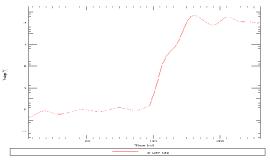

图2为该板第一板一典型总线网络中,驱动器的一近端负载的信号上升沿的测试波形,从图中可以看出,接收端的信号在上升沿的阈值处有畸变点,总线网络信号存在之一较普遍的现象,即图1中任一驱动端发出信号时,其近端接收端信号在上升/下降沿上出现信号畸变。

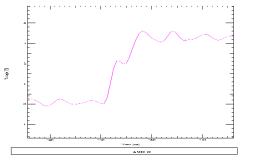

图2 总线网络一近端负载 的信号上升沿测试 波形

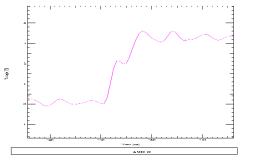

图3 总线网络 一近端负载的信号上升沿使用DF/SIGNOISE 的仿真波形

针对存在的问题,利用DF/SigNoise从器件选型和PCB布局布线等方面进行了较仔细的分析,图3为DF/SigNoise对同一网络的接收端的仿真结果,可以看出,仿真分析得到的信号波形与测试结果非常吻合,进一步分析表明,信号畸变的原因主要有两个方面,一是PCB总线布局布线存在一定问题,二是器件选型。 第一板总线采用的链式布局布线,近端接收端将承受远端重负载的反射,使得信号上升/下降沿上出现信号畸变。另外,器件较快的上升/下降时间将增大信号的畸变现象。

3、问题解决方案

针对存在信号的问题和产生的主要原因,提出了问题解决方案。由于该板的密度也很高,使得采用网络匹配的方案不适合于板问题的解决,主要考虑从PCB布局布线和器件选型两个方面解决信号存在的问题,布局布线上采用一种近似于星形的布局,布线上尽量是负载对称分布;器件选型本着在满足信号传输速率的前提下,尽量选用较慢上升/下降沿器件的原则,器件重新选用了上升/下降沿速度较低的另一型号。

最后,利用 DF/SigNoise 对采用该改进方案的设计板的信号完整性进行了制板前的 仔细分析验证。

图4为采用改进方案设计PCB板,DF/SigNoise仿真得到的一典型总线网络近端负载信号的上升沿波形,可以看出,改进方案有效地消除了信号的畸变。

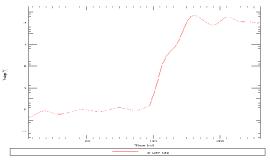

图4 总线网络一近端负载信号上升沿的仿真波形

图5 总线网络一近端负载信号上升沿的测试波形

图5为对应近端负载信号的上升沿的实际测试波形,从图中可以看出,实际测试得到的信号质量很好,而且与仿真波形非常吻合,符合设计要求。在信号的下降沿上也有相类似的结果,这里不再赘述。仿真改进方案使信号的上升沿和下降沿消除了畸变,单调性很好,仿真结果较精确地反映了实际信号质量,充分表明了新方案的正确性和可行性以及仿真手段对设计的指导作用。利用PCB信号完整性分析手段能有效地提高产品性能,大大地缩短产品开发周期, 目前该板已投入系统应用中。

三、结论

以上介绍了DF/SigNoise仿真工具在一通讯产品单板的PCB设计中的应用,利用DF/SigNoise解决单板设计中存在的信号完整性问题,从测试结果与仿真结果的比较可以看出,仿真结果较精确地反映了实际信号质量,仿真得到的改进方案使存在的问题得到了彻底解决。利用EDA工具,可提高产品性能,缩短设计周期,加强PCB设计的可行性和正确性,在模型质量有保证前提下,DF/SigNoise具有较高的仿真精度。

本文介绍了在通讯产品开发中,利用Cadence公司的DF/SigNoise信号完整性分析工具模 块解决 PCB 设计中存在的信号完整性(Signal Integrity)问题。

【关键词 】 PCB设计 信号完整性 (SI)

一、引言

当今通讯产业的蓬勃发展,得益于通讯产品的日新月异。高性能的产品开发,硬件设计,已不能仅靠年久的经验或器件使用说明来完成,工程师在设计高速数字信号传输系统时,要面临信号完整性(Signal Integrity)、电磁干扰(EMI)、时序(Timing)等问题,设计需要强 有力的EDA工具支持。DF/SigNoise是CADENCE公司的PCB信号完整性分析工具,可用于分析解决高速、高密度的互联线信号传输问题。本文介绍了利用Cadence公司的 DF/SigNoise 解 决通讯产品开发中,一块高密度、多负载PCB板总线网络存在的信号完整性问题,取得了较为满意的效果,解决了存在的信号质量问题,有效地缩短了产品开发周期。

二、PCB板的信号完整性仿真分析

1、硬件设计简介

图1为该板设计的主要总线网络结构,该板为系统中一主要的单板,数据总线、配置总线及使用的元器件很多,使得该板的密度较高。总线等网络的数据都是双向传输,且是点到多点,该板采用八层板结构,两层电源、地,六层信号。

2、信号存在问题及仿真分析

由于该板第一样板设计的时间短,使得设计中的器件选型和PCB的布局布线存在不足,第一板在测试中发现下列问题:总线网络中,近端负载信号波形在上升沿或下降沿上阈值处有畸变发生, 主要驱动器间的信号过冲很大等等。

图2为该板第一板一典型总线网络中,驱动器的一近端负载的信号上升沿的测试波形,从图中可以看出,接收端的信号在上升沿的阈值处有畸变点,总线网络信号存在之一较普遍的现象,即图1中任一驱动端发出信号时,其近端接收端信号在上升/下降沿上出现信号畸变。

图2 总线网络一近端负载 的信号上升沿测试 波形

图3 总线网络 一近端负载的信号上升沿使用DF/SIGNOISE 的仿真波形

针对存在的问题,利用DF/SigNoise从器件选型和PCB布局布线等方面进行了较仔细的分析,图3为DF/SigNoise对同一网络的接收端的仿真结果,可以看出,仿真分析得到的信号波形与测试结果非常吻合,进一步分析表明,信号畸变的原因主要有两个方面,一是PCB总线布局布线存在一定问题,二是器件选型。 第一板总线采用的链式布局布线,近端接收端将承受远端重负载的反射,使得信号上升/下降沿上出现信号畸变。另外,器件较快的上升/下降时间将增大信号的畸变现象。

3、问题解决方案

针对存在信号的问题和产生的主要原因,提出了问题解决方案。由于该板的密度也很高,使得采用网络匹配的方案不适合于板问题的解决,主要考虑从PCB布局布线和器件选型两个方面解决信号存在的问题,布局布线上采用一种近似于星形的布局,布线上尽量是负载对称分布;器件选型本着在满足信号传输速率的前提下,尽量选用较慢上升/下降沿器件的原则,器件重新选用了上升/下降沿速度较低的另一型号。

最后,利用 DF/SigNoise 对采用该改进方案的设计板的信号完整性进行了制板前的 仔细分析验证。

图4为采用改进方案设计PCB板,DF/SigNoise仿真得到的一典型总线网络近端负载信号的上升沿波形,可以看出,改进方案有效地消除了信号的畸变。

图4 总线网络一近端负载信号上升沿的仿真波形

图5 总线网络一近端负载信号上升沿的测试波形

图5为对应近端负载信号的上升沿的实际测试波形,从图中可以看出,实际测试得到的信号质量很好,而且与仿真波形非常吻合,符合设计要求。在信号的下降沿上也有相类似的结果,这里不再赘述。仿真改进方案使信号的上升沿和下降沿消除了畸变,单调性很好,仿真结果较精确地反映了实际信号质量,充分表明了新方案的正确性和可行性以及仿真手段对设计的指导作用。利用PCB信号完整性分析手段能有效地提高产品性能,大大地缩短产品开发周期, 目前该板已投入系统应用中。

三、结论

以上介绍了DF/SigNoise仿真工具在一通讯产品单板的PCB设计中的应用,利用DF/SigNoise解决单板设计中存在的信号完整性问题,从测试结果与仿真结果的比较可以看出,仿真结果较精确地反映了实际信号质量,仿真得到的改进方案使存在的问题得到了彻底解决。利用EDA工具,可提高产品性能,缩短设计周期,加强PCB设计的可行性和正确性,在模型质量有保证前提下,DF/SigNoise具有较高的仿真精度。